# SiTCP 入出力ポート解説書

第 1.0.4 版

2021年10月14日

(株)Bee Beans Technologies

# 改版履歴

| 版数    | 日付         | 内容 |

|-------|------------|----|

| 1.0.4 | 2021/10/14 | 初版 |

|       |            |    |

|       |            |    |

|       |            |    |

# 【目次】

| . 概: | 安    |                                          | . 1 |

|------|------|------------------------------------------|-----|

| . 信- | 号の訪  | 党明                                       | . 1 |

| 2.1. | シス   | ペテムインタフェース                               | . 1 |

| 2.2. | ネッ   | トワークパラメータ設定インタフェース                       | . 2 |

| 2.2  | 2.1. | FORCE_DEFAULTn                           | . 3 |

| 2.2  | 2.2. | TCP ポート関連信号                              | . 3 |

| 2.2  | 2.3. | TCP_SERVER 関連信号                          | . 3 |

| 2.3. | EE   | PROM インタフェース                             | . 4 |

| 2.4. | ュー   | - ザ設定用レジスタ                               | . 4 |

| 2.5. | MI   | I/GMII インタフェース                           | . 5 |

| 2.6. | TC   | P インタフェース・セッション関連信号                      | . 6 |

| 2.6  | 3.1. | 接続相手によるセッション切断時のシーケンス(サーバーモード)           | . 7 |

| 2.6  | 3.2. | SiTCP によるセッション切断時のシーケンス(サーバーモード)         | . 7 |

| 2.6  | 3.3. | セッション開始および接続相手による切断時のシーケンス(クライアントモード)    | . 8 |

| 2.6  | 3.4. | セッション開始および SiTCP による切断時のシーケンス(クライアントモード) | . 8 |

| 2.7. | TC   | P インタフェース・データ送受信関連信号                     | . 9 |

| 2.7  | 7.1. | TCP データ送信                                | . 9 |

| 2.7  | 7.2. | TCP データ受信                                | 10  |

| 2.8. | RB   | CP インタフェース                               | 12  |

| 2.8  | 3.1. | RBCP インタフェースによる書き込み                      | 12  |

| 2.8  | 3.2. | RBCP インタフェースによる読み込み                      | 13  |

| 参    | 考文菌  | <del>†</del>                             | 14  |

# 1. 概要

本文書は、内田智久博士が作成した文書「SiTCP 説明書」「SiTCP ライブラリ」の補足資料であり、SiTCP の入出力ポートを解説するものです。SiTCP は内田智久博士が開発し、(株)Bee Beans Technologies(以下 BBT)が管理・配布を行っているネットワーク・プロセッサです。

# 2. 信号の説明

SiTCP の入出力ポートについて説明します。

# 2.1. システムインタフェース

表 2-1 にシステムインタフェース関連の信号を示します。

信号名 I/O 同期クロック 説明 システムクロック 推奨動作周波数は 130MHz 以上 CLK(100Mbps以下のリンクで動作させる場合15MHz以上を推 Ι 奨) RST非同期 SiTCP に対する非同期リセット(1 でリセット) Ι TIM 1US 1 μs に CLK の 1 パルス幅 1 となるタイミング信号 Ι  $TIM_{1}MS$ 1ms に CLK の 1 パルス幅 1 となるタイミング信号 Ι  $TIM_1S$ Ι CLK1 秒に CLK の 1 パルス幅 1 となるタイミング信号 1分に CLK の 1 パルス幅 1 となるタイミング信号 (※1) TIM\_1M Ι SiTCP\_RST SiTCP のリセットおよび初期化中に 1 となる信号(※2)(※3) O

表 2-1 システムインタフェース関連信号

- ※ 1: 現在使用していませんが、将来の互換性確保のため接続してください。

- ※ 2: RST 解除後も一定時間 1 を保持します。外部回路のリセットとして使用可能です。

- ※ 3: 内部レジスタによるリセット書き込み後にも一定時間 1 となります(SiTCP 内部レジスタ解説書を参照)。

# 2.2. ネットワークパラメータ設定インタフェース

表 2-2 にネットワークパラメータ設定インタフェース関連の信号を示します。また、2.2.1~2.2.3 に FORCE\_DEFAULTn、TCP ポート関連信号および TCP\_SERVER 関連信号の詳細を記載します。

表 2-2 ネットワークパラメータ設定インタフェース関連信号

| 信号名                           | I/O | 同期クロック | 説明                             |

|-------------------------------|-----|--------|--------------------------------|

| FORCE_DEFAULTn                | I   | CLK    | 0で ForceDefault 状態に設定          |

| MY_MAC_ADDR[47:0]             | О   | CLK    | 使用中の MAC アドレスの値                |

| IP_ADDR_IN[31:0]              | I   | 非同期    | IP アドレス設定 (※1)                 |

| IP_ADDR_DEFAULT[31:0]         | О   | CLK    | IP アドレス用レジスタの値                 |

| TCP_MAIN_PORT_IN[15:0]        | I   | 非同期    | TCP メインポート設定 (※1)              |

| TCP_MAIN_PORT_DEFAULT[15:0]   | О   | CLK    | TCP メインポート用レジスタの値              |

| TCP_SUB_PORT_IN[15:0]         | I   | 非同期    | TCP サブポート設定 (※1)               |

| TCP_SUB_PORT_DEFAULT[15:0]    | О   | CLK    | TCP サブポート用レジスタの値               |

| RBCP_PORT_IN[15:0]            | I   | 非同期    | RBCP ポート設定 (※1)                |

| RBCP_PORT_DEFAULT[15:0]       | О   | CLK    | RBCP ポート用レジスタの値                |

| TCP_SERVER_MAC_IN[47:0]       | I   | 非同期    | 接続先サーバーの MAC アドレス (※1)         |

| TCP_SERVER_MAC_DEFAULT[47:0]  | О   | CLK    | 接続先サーバーの MAC アドレス<br>用レジスタの値   |

| TCP_SERVER_ADDR_IN[31:0]      | I   | 非同期    | 接続先サーバーの IP アドレス<br>(※1)       |

| TCP_SERVER_ADDR_DEFAULT[31:0] | О   | CLK    | 接続先サーバーの IP アドレス用<br>レジスタの値    |

| TCP_SERVER_PORT_IN[15:0]      | I   | 非同期    | 接続先サーバーの TCP ポート (※1)          |

| TCP_SERVER_PORT_DEFAULT[15:0] | О   | CLK    | 接続先サーバーの TCP ポート用<br>レジスタの値    |

| PHY_ADDR[4:0]                 | I   | 非同期    | PHY デバイスの MIF アドレスを<br>設定 (※2) |

| MIN_RX_IPG[3:0]               | I   | 非同期    | TCP 受信時の最小パケット間隔 (IPG)         |

<sup>※ 1:</sup> 対応する専用レジスタ(DEDAULT で終わる信号)に接続することで、初期値の設定および RBCP レジスタを介した確認・設定ができます。

<sup>※ 2:</sup> PHY デバイスのデータシートを確認の上、設定してください。

#### 2.2.1. FORCE\_DEFAULTn

ForceDefault 状態を設定するためのポート(負論理)です。このポートの値は SiTCP\_RST 解除前に確定される必要があります。ForceDefault 状態とは、評価や設定を目的としたライセンスなしで動作可能な状態であり、1 台の SiTCP と PC の閉じたネットワークでのみ使用可能です。初期設定や設定した IP アドレス等が不明の場合にも使用できます。ForceDefault 状態では MAC アドレスが固定されるとともに、IP アドレス・ポート番号のレジスタ値は初期値に設定されます(表 2-3)。

| 項目           | 設定値               |

|--------------|-------------------|

| MAC アドレス     | 02:00:C0:A8:00:10 |

| IP アドレス(※)   | 192.168.10.16     |

| TCP ポート番号(※) | 24                |

| RBCPポート番号(※) | 4660              |

表 2-3 ForceDefault 状態

※ MAC アドレスを除きこれらの値はレジスタの初期値です。ポートから任意の値を設定できます。

#### 2.2.2. TCP ポート関連信号

SiTCP が確立できるのは 1 セッションですが、2 ポートまで設定可能であり、一方をメインポート、もう一方をサブポートと称しています。メインポート番号は TCP\_MAIN\_PORT\_IN へ、サブポート番号は TCP\_SUB\_PORT\_IN へ入力します。なお、1 ポートのみ使用する場合はメインポートを使用し、サブポート番号は 0 を入力してください。また、サブポートはクライアントモード(後述 2.6 を参照)では使用できません。

# 2.2.3. TCP\_SERVER 関連信号

後述 2.6 のクライアントモードを使用する場合、TCP\_SERVER で始まり IN で終わる信号(TCP\_SERVER\_MAC\_IN 等)にサーバーとする接続先の MAC アドレス、IP アドレスおよび TCP ポート番号を設定してください。また、対応する専用レジスタ(TCP\_SERVER で始まり DEDAULT で終わる信号)と接続することで、初期値の設定および RBCP レジスタを介した確認・設定ができます。

SiTCP 内部レジスタ 0xFFFF\_FF10 の bit6(Client ARP)を 1 に設定している場合は、TCP\_SERVER\_MAC\_IN の値は使用しません。詳細は「SiTCP 内部レジスタ解説書」を参照してください。

# 2.3. EEPROM インタフェース

表 2-4 に EEPROM インタフェース関連の信号を示します。これらは CLK の同期信号であり、AT93C46D(SiTCP の設定情報やライセンス情報を格納するための不揮発性メモリ)に接続します。接続する AT93C46D の ORG ピンは GND に接続し、X8 モードとして下さい。

なお、評価用として ForceDefault 状態でのみ使用する場合は EEPROM\_DO に 1 を入力し、他のポートはオープンとしてください。

| 信号名       | I/O | 同期クロック | 説明                    |  |  |

|-----------|-----|--------|-----------------------|--|--|

| EEPROM_CS | О   | CLK    | AT93C46D の CS 端子に接続   |  |  |

| EEPROM_SK | О   |        | AT93C46D の SK 端子に接続   |  |  |

| EEPROM_DI | О   |        | AT93C46D の DI 端子に接続   |  |  |

|           |     |        | AT93C46D の DO 端子に接続   |  |  |

| EEPROM_DO | I   |        | 外部または FPGA にてプルアップしてく |  |  |

|           |     |        | ださい。                  |  |  |

表 2-4 EEPROM インタフェース関連信号

#### 2.4. ユーザ設定用レジスタ

表 2-5 にユーザ設定用レジスタ関連の信号を示します。これらは CLK の同期信号です。 EEPROM(AT93C46D)のレジスタ  $0xFFFF_FC3C \sim 0xFFFF_FC3F$  への設定値がこの領域に反映されます(ユーザが任意に値を設定できます)。FPGA へ設定が反映されるのは SiTCP\_RST が解除された後となります。

| 信号名              | I/O | 同期クロック | 説明         |

|------------------|-----|--------|------------|

| USR_REG_X3C[7:0] | О   |        | ユーザ設定用レジスタ |

| USR_REG_X3D[7:0] | О   | CLK    | ユーザ設定用レジスタ |

| USR_REG_X3E[7:0] | О   | CLK    | ユーザ設定用レジスタ |

| USR_REG_X3F[7:0] | О   |        | ユーザ設定用レジスタ |

表 2-5 ユーザ設定用レジスタ関連信号

# 2.5. MII/GMII インタフェース

表 2-6に MII/GMII インタフェースに関連する信号を示します。

表 2-6 MII/GMII インタフェース関連信号

| 信号名           | I/O | 同期クロック      | 説明                                        |

|---------------|-----|-------------|-------------------------------------------|

| MODE CMII     | т   | 非同期         | 1 で PHY のレジスタへ 1000BASE-T を有効にす           |

| MODE_GMII     | Ι   |             | る設定を行う(MII のみ使用する場合は 0 を設定)               |

|               |     | 非同期         | MII/GMII 動作の選択信号 (※1)                     |

| GMII_1000M    | I   |             | 1 : Gigabit Ethernet (GMII) / 0 : 100Mbps |

|               |     |             | Ethernet(MII)                             |

| GMII_RSTn     | О   | CLK         | PHY デバイスのリセットに接続、0 でリセット                  |

|               |     | _           | MII 動作の時は PHY デバイスの TX_CLKを入力             |

| GMII_TX_CLK   | I   |             | (%2)                                      |

| GMII_IA_CLK   | 1   |             | GMII 動作の時は FPGA 内で生成した GTX_CLK            |

|               |     |             | と同じ 125MHz を入力 (※3)                       |

| GMII_TX_EN    | О   |             | PHY デバイスの TX_EN に接続                       |

| GMII_TXD[7:0] | О   | GMII_TX_CLK | PHY デバイスの TXD[7:0]に接続 (※4)                |

| GMII_TX_ER    | О   |             | PHY デバイスの TX_ER に接続                       |

| GMII_RX_CLK   | I   | _           | PHY デバイスの RX_CLK に接続(※2)                  |

| GMII_RX_DV    | I   |             | PHY デバイスの RX_DV に接続                       |

| GMII_RXD[7:0] | I   | GMII_RX_CLK | PHY デバイスの RXD[7:0]に接続 (※5)                |

| GMII_RX_ER    | I   |             | PHY デバイスの RX_ER に接続                       |

| GMII_CRS      | I   | +-□+u       | PHY デバイスの CRS に接続                         |

| GMII_COL      | I   | 非同期         | PHY デバイスの COL に接続                         |

| GMII_MDC      | О   |             | PHY デバイスの MDC に接続                         |

| GMII_MDIO_IN  | I   |             | PHY デバイスの MDIO に接続                        |

| GMII_MDIO_OUT |     | CLK         | 3ステートバッファを介して PHY デバイスの MDIO              |

| GMII_MDIO_OUT | О   |             | に接続                                       |

| GMII_MDIO_OE  | О   |             | GMII_MDIO_OUT の 3 ステートバッファ制御信号            |

- ※ 1: GMII では 1000BASE-T で動作し、MII ではそれ以外(100BASE-TX または 10BASE-T)で動作します。GMII 動作中は PHY の RX CLK が 125MHz となります。

- ※ 2: PHY デバイスの TX\_CLK と RX\_CLK は FPGA のクロック入力専用ピンに接続してください。

- ※ 3: GMIIとMIIを切り替えて使用する場合は、BUFGMUXまたは同等のプリミティブを使用してGMII\_TX\_CLKとGTX\_CLK(またはそのソースクロック)を切り替えてください。

- ※ 4: MII のみ対応の PHY 使用時 GMII\_TXD[7:4]は使用しないため未接続としてください。

- ※ 5: MII のみ対応の PHY 使用時 GMII\_RXD[7:4]は使用しないため 0 を入力してください。

#### 2.6. TCP インタフェース・セッション関連信号

表 2-7 に TCP インタフェース・セッション関連信号を示します。

セッション相手からの接続要求で受動的にセッションを確立するモードをサーバーモード、SiTCP から接続するモードをクライアントモードと呼びます。いずれのモードでも、セッションが確立すると OPEN\_ACK(サーバーモードでは MAIN\_OPEN\_ACK、クライアントモードでは SUB\_OPEN\_ACK)が 1、切断されると 0 になり、接続先からのセッション切断要求があると CLOSE\_REQ が 1 になります。セッション切断時のシーケンスを  $2.6.1 \sim 2.6.4$  に示します。

サーバーモードでセッションを切断する場合は  $CLOSE\_ACK$  を 1 にします。 $CLOSE\_ACK$  は、 $CLOSE\_REQ$  と  $MAIN\_OPEN\_ACK$  が 0 になるまで 1 を継続して下さい。セッション相手 からの切断要求で切断する場合は  $CLOSE\_REQ$  を直接または必要なタイミングの待ち合わせ回路を経由して  $CLOSE\_ACK$  に接続します。

クライアントモードでセッションを開始する時は OPEN\_REQ を 1 に設定し、切断する場合は 0 に設定します (OPEN\_REQ を 1 にした後にセッションが確立できない場合は、 TCP\_OPEN\_ERROR が 1 となります)。 CLOSE\_REQ が 1 になった場合は接続先からセッション切断要求が送られてきているため、 OPEN\_REQ を 0 にすることが求められます。 なお、 クライアントモードでは TCP メインポートのみ使用可能であり、 サブポートは使用できません。

接続先からのセッション切断要求を受信しても、SiTCP は送信バッファが空になるまでセッションを維持しようとします。この時、データを送信すると相手から強制的にセッションを切断されることがありますが、異常ではありません。

また、クライアントモードで使用する場合は、サーバーMAC アドレス・IP アドレス・TCP ポート番号を設定する必要があります(2.2 参照)。

信号名 Ⅰ/〇 | 同期クロック 説明 クライアントモードでセッション開始要求時に 1、セッ OPEN\_REQ Ι ション切断要求時に0とする信号(※1) MAIN\_OPEN\_ACK メインポートでのセッション確立時に1となる信号 SUB\_OPEN\_ACK サブポートでのセッション確立時に1となる信号(※2) O クライアントモードで SiTCP からセッション切断後、 CLK MSL タイマ(※3)が満了する前に OPEN\_REQ を TCP\_OPEN\_ERROR 0 1にした場合1となる信号 セッション切断要求(FIN)の受信時に1となる信号 CLOSE\_REQ O サーバーモードでセッション切断を指示する場合に1 CLOSE\_ACK Ι とする信号

表 2-7 TCP インタフェース・セッション関連信号

※ 1: サーバーモードでは0を入力してください。

※ 2: クライアントモード時はサブポートを使用できないため変化しません(0 固定)。

※ 3: SiTCP 内部レジスタ解説書を参照してください。

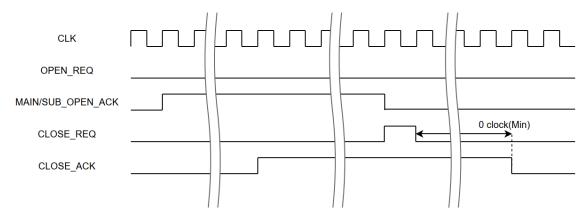

# 2.6.1. 接続相手によるセッション切断時のシーケンス(サーバーモード)

サーバーモードでは接続相手から切断要求があると CLOSE\_REQ が 1 になり、その後 MAIN/SUB\_OPEN\_ACK が 0 となります。CLOSE\_REQ は直接、または必要なタイミングの待ち合わせ回路を経由して CLOSE\_ACK に接続してください(図 2-1)。

図 2-1 接続相手によるセッション切断時のシーケンス(サーバーモード)

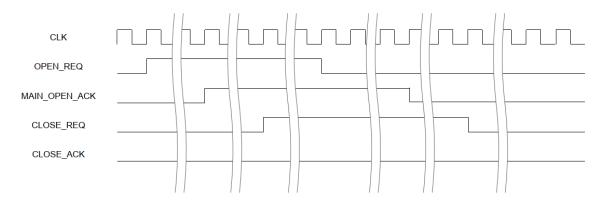

#### 2.6.2. SiTCP によるセッション切断時のシーケンス(サーバーモード)

サーバーモードで SiTCP からセッションを切断する場合は  $CLOSE\_ACK$  を 1 にします。  $CLOSE\_ACK$  は  $MAIN/SUB\_OPEN\_ACK$  および  $CLOSE\_REQ$  が 0 になるまで 1 を継続して下さい(図 2-2)。

図 2-2 SiTCP によるセッション切断時のシーケンス(サーバーモード)

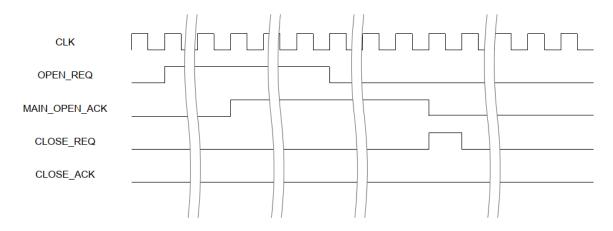

# 2.6.3. セッション開始および接続相手による切断時のシーケンス(クライアントモード)

クライアントモードにおいて、接続相手から切断要求があると CLOSE\_REQ が 1 になります。このとき、OPEN\_REQ を 0 にすることによって要求に応答します。(図  $2 \cdot 3$ )。

図 2-3 接続相手によるセッション切断時のシーケンス(クライアントモード)

# 2.6.4. セッション開始および SiTCP による切断時のシーケンス(クライアントモード)

クライアントモードにおいて、SiTCP からセッションを切断する場合は  $OPEN_REQ$  を 0 にします(図 2-4)。

図 2-4 SiTCP によるセッション切断時のシーケンス(クライアントモード)

# 2.7. TCP インタフェース・データ送受信関連信号

表 2-8 に TCP インタフェース・データ送受信関連信号を示します。

表 2-8 TCP インタフェース・データ送受信関連信号

| 信号名             | I/O | 同期クロック | 説明                          |

|-----------------|-----|--------|-----------------------------|

| TX_WR           | I   |        | 1 で送信データ書き込みイネーブル           |

| TX_DATA[7:0]    | I   |        | 送信データ                       |

| TX_FULL         | О   |        | 送信バッファの Almost Full フラグ確立時に |

|                 |     |        | 1となる信号(※1)                  |

| TCP_TX_OW_ERROR | О   |        | 送信バッファへの上書きエラ一時に1となる信       |

|                 |     | CLK    | 号(※2)                       |

| TX_FILL[15:0]   | О   |        | 送信バッファに格納されているデータバイト数       |

| RX_WR           | О   |        | 1 で受信データ有効                  |

| RX_DATA[7:0]    | О   |        | 受信データ                       |

| RX_FILL[15:0]   | I   |        | 受信バッファに格納されているデータバイト数       |

※ 1: 送信データ格納数が「送信バッファ容量(32KB)-32Byte」を超えると1になる信号です。

※ 2: 送信データ格納数が「送信バッファ容量(32KB)-16Byte」を超えると1になる信号です。

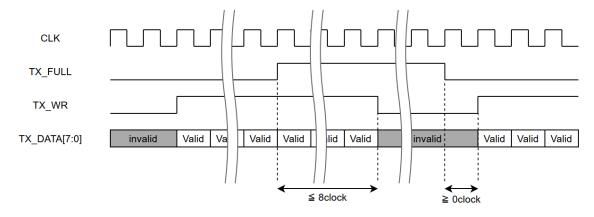

# 2.7.1. TCP データ送信

TCP データ送信のフロー制御について図 2-5 に示します。TCP コネクションが確立し MAIN/SUB\_OPEN\_ACK=1 の時のみデータの書き込みが可能です。送信データの書き込みは同期 FIFO メモリと同じインタフェースであり、 $TX_WR \ge TX_DATA[7:0]$ を使用します。CLK に同期させ送信データを  $TX_DATA[7:0]$ に設定し、 $TX_WR=1$  にすると送信バッファに書き込まれます。同期回路ですので CLK の立ち上がりエッジ毎に 1 バイトのデータ と見なされます。

TCPコネクション確立状態、かつ TX\_FULL=0 の時にデータを書き込むことができます。 TX\_FULL=1 になった場合、8 クロック以内に TX\_WR=0 にして書き込みを中断してください。 TX\_FULL=0 になったら書き込みを再開することが出来ます。 TCP コネクションが確立されている間に以上を繰り返してください。

図 2-5 TCP データ送信のフロー制御

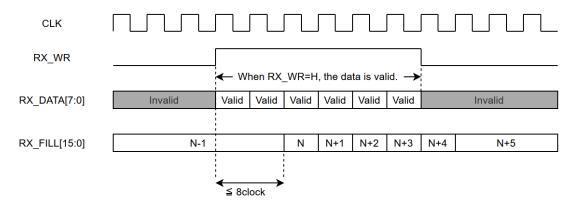

#### 2.7.2. TCP データ受信

SiTCP の TCP 受信機能を使用する場合、Xilinx 社のツールである ISE Design Suite の [Core Generator]-[FIFO Generator]、または Vivado Design Suite の [IP Catalog]-[FIFO Generator]で作成した受信バッファ用の FIFO メモリをユーザ回路と SiTCP 間に配置し、各信号を接続します。FIFO メモリの設定について表 2-9 に、TCP データ受信のフロー制御について図 2-6 に示します。

SiTCPはRX\_DATA[7:0]に受信データを受信順に置き、RX\_WR=1にして有効データを 受信したことを通知します。RX\_DATA[7:0]を同期 FIFO の書き込みデータ端子に、 RX WR を書き込みイネーブル端子に接続してください。

また、RX\_FILL[15:0]により受信バッファのデータ格納数をデータ受信後 8 クロック以内に通知してください(これが TCP ウィンドウサイズとして反映されます)。RX\_FILL[15:0]は同期 FIFO の Data count 端子に下位ビットから接続し、未使用ビットは全て 1 を設定してください。例えば、受信 FIFO が 16KB の容量の時、Data count 端子は 14bit になります。従って RX\_FILL[13:0]= Data count[13:0]を接続し、RX\_FILL [15:14]のビットに 1 を設定してください(Verilog HDL は RX\_FILL [15:14] = 2' b11;となります)。

TCP 受信機能を使用しない場合は RX\_FILL [15:0]に 0 を設定してください。他の値を設定しても動作しますが 0 設定を奨励します。

項目 設定

書き込みデータ bit 幅 8bit

Data count オプション 有効、bit 幅を最大に設定

FIFO 深さ 4KB 以上 64KB 以下(2 のべき乗)

表 2-9 FIFO メモリ設定

図 2-6 TCP データ受信のフロー制御

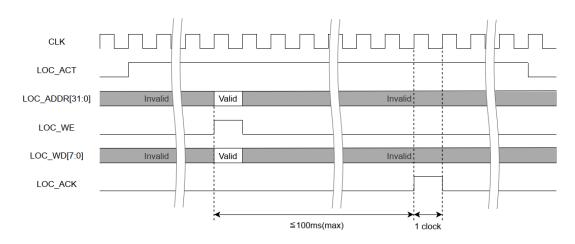

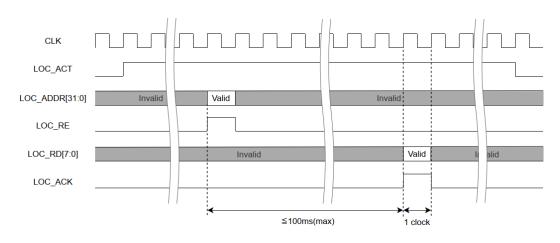

#### 2.8. RBCP インタフェース

表 2-10に RBCP インタフェース関連信号を示します。RBCP インタフェースは、UDP のコマンドでバスマスタとして動作するインタフェースです。RBCP インタフェースも CLK に同期して動作します。一つのコマンドで最大 255 個のバスサイクルが発生します。一つのコマンドが開始すると LOC\_ACT が 1 になり、一つのコマンドが終了するまで 1 を継続します。コマンドが終了するかタイムアウトすると LOC\_ACT=0 になります。タイムアウト時間はバスサイクル数に関わらず、1 コマンドあたり約 100ms です。バスサイクルは LOC\_WE または LOC\_RE が 1 クロック 1 になったところから、ユーザ回路が LOC\_ACK を 1 クロック 1 にするところまでです。なお、RBCP アドレス 0xFFFFF0000 から 0xFFFFFFFF は SiTCP 内部レジスタ用に予約

なお、RBCP アドレス 0xFFFF0000 から 0xFFFFFFFF は SiTCP 内部レジスタ用に予約されていますので(SiTCP 内部レジスタ解説書を参照)、このアドレス以外を使用してください。

| 信号名            | I/O | 同期クロック | 説明                  |

|----------------|-----|--------|---------------------|

| LOC_ACT        | О   |        | バスサイクルが実行中に 1 となる信号 |

| LOC_ADDR[31:0] | О   |        | アクセス中のアドレス          |

| LOC_WE         | О   |        | 書き込みアクセス時に 1 となる信号  |

| LOC_WD[7:0]    | O   | CLK    | 書き込みデータ             |

| LOC_RE         | O   |        | 読み込みアクセスに 1 となる信号   |

| LOC_RD[7:0]    | I   |        | 読み込みデータ             |

| LOC_ACK        | I   |        | 1でアクセス終了応答          |

表 2-10 RBCP インタフェース関連信号

#### 2.8.1. RBCP インタフェースによる書き込み

RBCP インタフェースによる書き込みアクセスを図 2-7 に示します。SiTCP は PC からの書き込みコマンドを受信した時、 $LOC\_ADDR[31:0]$  にアクセスするアドレス、 $LOC\_WD[7:0]$ に書き込みデータを設定すると同時に、 $LOC\_WE=1$  として書き込み動作であることをユーザ回路に通知します。ユーザ回路は該当するアドレスへの書き込みが終了したら  $LOC\_ACK$  を 1 クロックのみ 1 にして応答する必要があります。

該当回路がないアドレスをアクセスした場合等は LOC\_ACK が 0 のままになりますが、 待ち時間が約  $100 \mathrm{msec}$  を超えた時点で SiTCP はエラーと判断してバスサイクルを終了し、 PC に対してエラーを通知するパケットを送ります。

図 2-7 RBCP インタフェースによる書き込みアクセス

# 2.8.2. RBCP インタフェースによる読み込み

RBCP インタフェースによる読み込みアクセスを図 2-8 に示します。SiTCP は PC からの読み込みコマンドを受信した時、 $LOC\_ADDR[31:0]$ にアクセスするアドレスを設定すると同時に  $LOC\_RE=1$  として読み込み動作であることをユーザ回路に通知します。ユーザ回路は該当するアドレスのデータを  $LOC\_RD[7:0]$ に設定すると同時に  $LOC\_ACK$  を 1 クロックのみ 1 にして応答する必要があります。

なお、読み込みの場合も ACK 応答時間が約 100msec を超えると SiTCP はエラーと判断してバスサイクルを終了し、PC ヘエラーを通知するパケットを送ります。

図 2-8 RBCP インタフェースによる読み込みアクセス

# 3. 参考文献

SiTCP 説明書 内田智久/BBT SiTCP 内部レジスタ解説書 BBT